Blog

本記事は、2023年に勤務された村瀬秀太さんによる寄稿です。

はじめに

はじめまして、京都大学 M1 の村瀬秀太です。普段は集積回路系の研究室でデバイスモデリングなどの研究をしています。ここではPFNでの業務経験について簡単に紹介します。

背景

皆さん大好きMN-Core™はPreferred Networks社が開発している深層学習アクセラレータです。スパコンの消費電力あたりの性能の順位を示すGreen500で3度も1位を取るなど、低消費電力なプロセッサーとしても知られています。しかし、そんなMN-Coreであっても電源を供給することは一筋縄ではいきません。

こんにちのHPC向けのプロセッサの多くは、1V程度の電圧があれば動作しますが、数十Aを超える電流を消費します。これはMN-Coreも例外ではありません。低電圧で大電流を供給するのは大変で、以下のような問題が発生します。

- 銅箔の抵抗によってMN-Coreに供給される電圧が下がってしまう

- 電磁ノイズが発生し、回路が正常に動作しなくなる

つまり、こういった現象を踏まえた基板設計が必要となるわけです。最終的には、このようなシミュレーションをMN-Core™上で行うことができれば理想的です。が、そこまでを短期間に実装するのは現実的ではないため、今回のプロジェクトではOSSを使った枠組み、プロトタイプを実装しました。

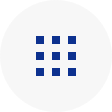

図1: PCB解析の流れ

順に説明します。

1. ガーバー/ドリルデータをパースする

まず、基板を解析するにあたっては基板の形状を取得する必要があります。そこで利用するのがガーバー/ドリルデータです。

ガーバー/ドリルデータは、基板設計CADが出力する、基板製造用のファイルです。ガーバーデータには基板の銅箔などのパターンが、ドリルデータにはドリル穴の位置やドリル径がそれぞれ含まれています。これらのファイルをパースすることで基板の具体的な形状や端子の情報を得ることができます。

本プロジェクトでは、python上で実装されているpcb-toolsというライブラリを用いました。pcb-toolsにはガーバー/ドリルデータをパースする機能が実装されているため、それを利用して次に紹介するgmshのAPIを叩くよう改造しました。

2. パターンに合わせたメッシュを生成する

有限要素法を行うためには、取得した基板の形状に合わせてメッシュを生成する必要があります。ここでいうメッシュは格子状のものではなく、2次元の場合は主に三角形が使われます。

有限要素法のためにメッシュを生成するためのOSSとして、gmshがよく知られています。gmshは3次元メッシュジェネレータで、pythonを含む様々な言語のAPIが提供されています。ここでは、基板のパターンをもとに2次元のメッシュを生成します。

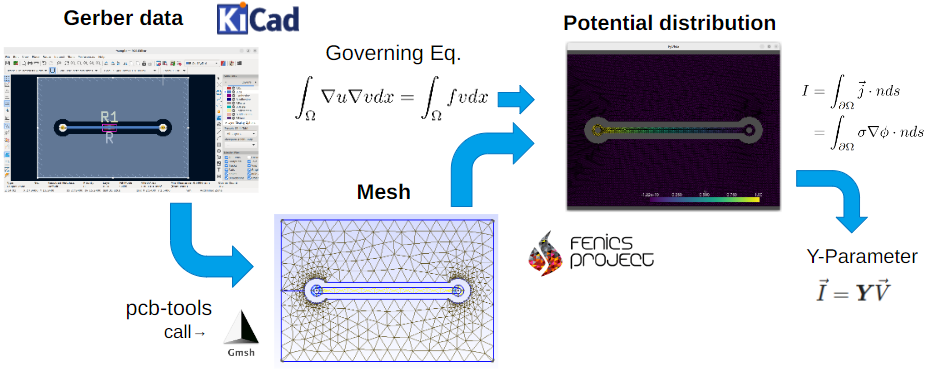

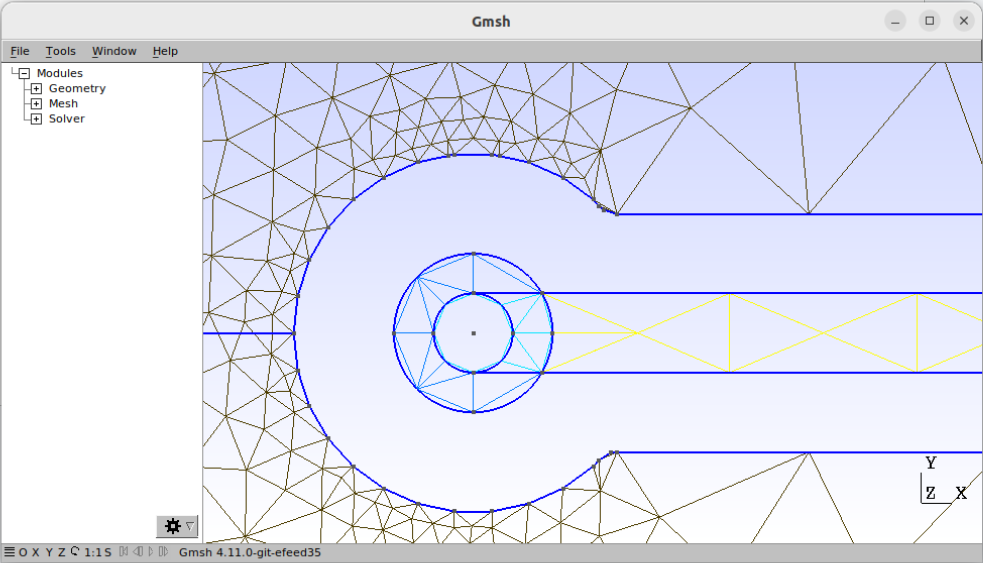

もう少し具体的に説明します。pcb-tools内部ではパターンは簡単な図形(円、直線など)に切り分けて処理されています。ですので、まずはそれらの図形をgmsh上で再現します。再現すると以下のような状態になります。

図2: 各要素図形を描画した結果

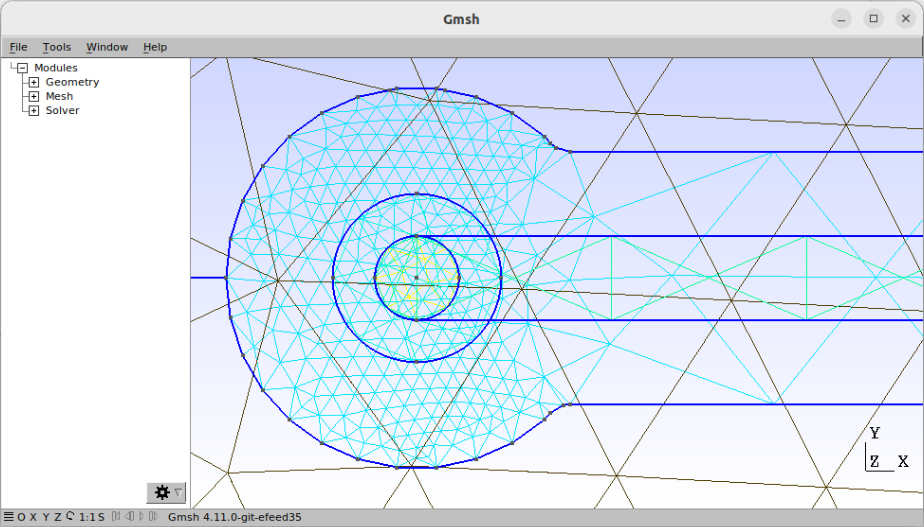

続いて(pcb-toolsの処理が終わってから)、これらの図形を組み合わせてパターンを形成します。具体的には以下の図のように、各図形要素の論理和を取ります(gmsh.model.occ.fraction)。ドリル穴は別途配列で管理し、差分を取ります(gmsh.model.occ.cut)。

図3: 図形の組み合わせ方の例

ドリル穴を開ける辺りは、処理の効率化に凝りだすときりがない(図形の内外判定を行い、関係ない差分処理を省くなど)のですが、シンプルな実装でもそれなりに速く動作してくれたため、単純な実装になっています。この処理を行うと、下図のようなメッシュが得られます。

図4: 図形を組み合わせた結果

3. 有限要素法でシミュレーションを行う

本プロジェクトでは、有限要素法を行うためにFEniCSを用いました。

まず、gmshで生成したメッシュをインポートして、Sobolev関数空間を定義します。Sobolev空間はBanach空間のようなもので、ノルムが定義できる関数全体の空間で、関数の値を評価するために重要な概念ではあります。

続いて、境界条件を指定します。2階の偏微分方程式においては、Dirichlet条件とNeumann条件の2つがよく知られています。今回の文脈では、これらはそれぞれ境界上の電圧と、境界から湧き出す(あるいは吸い込まれる)電流に対応します。FEniCSでは、条件を指定しない境界に関しては、湧き出しが0のNeumann条件、つまり電流が流れ出さない、という条件が適用されます。

今回は、各端子の電圧を指定し、電圧の分布や各端子の電流を求めることにしました。つまり、各端子にDirichlet条件を適用することになります。FEniCSでは、境界条件は境界上の値と境界か否かを判定する関数(np.isclose()などを使用)の組として定義します。ドリルファイルから端子に対応するスルーホールの座標や径を読み取り、境界条件を定義しました。

最後に偏微分方程式の形を定義して、方程式を解きます。FEniCSではuflという、微分方程式を表現するためのDSLが用意されており、これを用いて記述します。

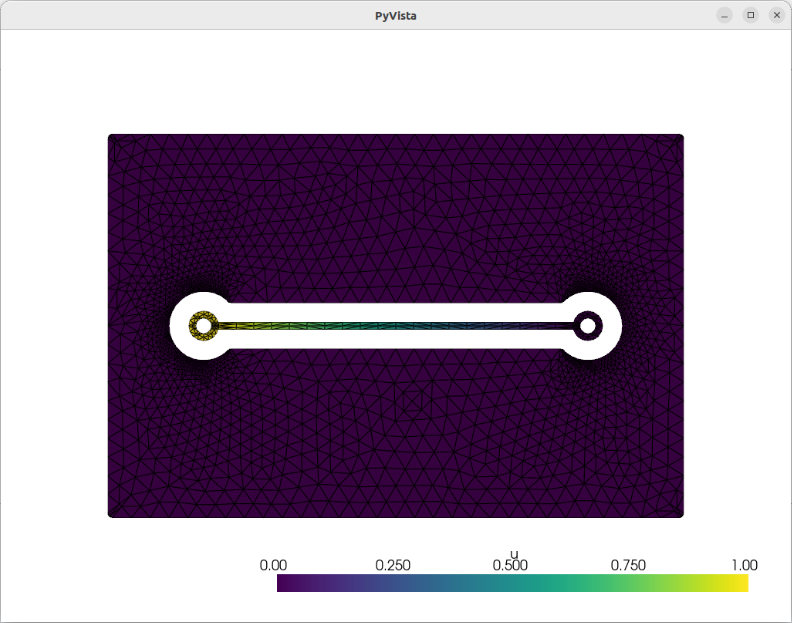

また、FEniCSはpyvistaによる解析結果の図示に対応しています。というわけで、いくつかの基板の解析結果(電圧分布)を貼っておきます。

図5: 解析結果の例

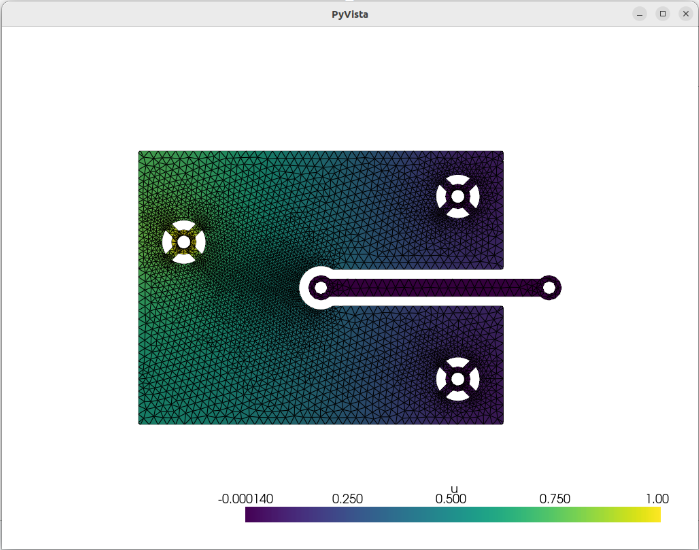

以下のように、ベタパターンも解析することができます。

図6: 解析結果(ベタパターンの場合)

結果から基板のYパラメータを抽出する

ここまで行ってきたシミュレーションの結果を回路設計に反映するには、解析結果から基板のパラメータを抽出するのが望ましいです。FEniCSによる解析を回路シミュレータと組み合わせて行うこともできなくはないのですが、どうしても計算に時間がかかってしまいます。

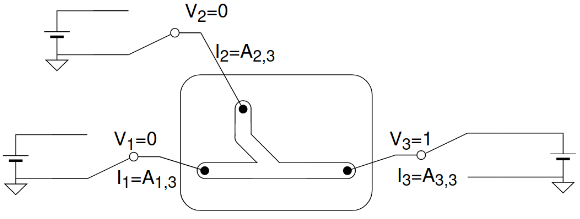

本プロジェクトでは基板の寄生抵抗にのみ注目している(基板を線形な対象として扱っている)ため、基板の特性をY-パラメータ(アドミタンス行列)という形で抽出することができます。Y-パラメータを用いることで、基板の特性をSPICEなどの回路シミュレーターで扱うことができ、効率の良いシミュレーションができます。具体的には、下図のように、基板の各端子にOne-hotになるように単位電圧(1V)を印加します。このとき、各端子に流れる電流の値を測定すると、Y-パラメータの各値が求まります。

図7: Yパラメータの取得方法

各端子の電流は、各端子の境界線上の電流密度の法線成分を積分すれば求まります。これは微分方程式と同様にuflで記述することで求めることができます。

解析結果の検証

さて、ここまで電流の解析を行ってきましたが、この結果は正しいのでしょうか。図示した結果はそれらしくは見えるのですが、果たして正しい電流の値が求まっているのでしょうか。

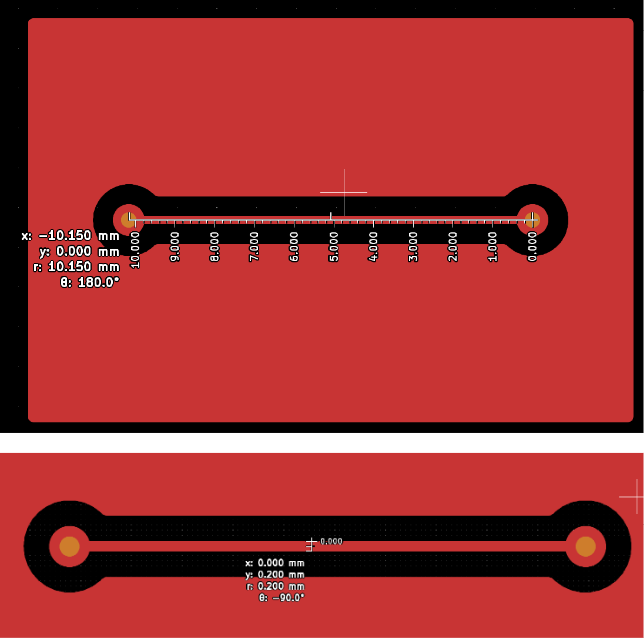

以下の基板データを用いて検証してみましょう。2つの端子の間の距離がおよそ10mm, 配線幅が0.2mmの基板で解析を行ってみます。なお、gmshでメッシュの細かさを指定することができるのですが、電流の値の精度はこの細かさに大きく左右されることになります。そのため、メッシュの細かさを6段階で変化させ、結果を比較します。

図8: 検証に用いる基板

電流の値は理論値と比較したいところですが、PCBのパターンはほとんどの場合形状が複雑で、理論値を求めるのが非常に困難です。今回は幅0.2mm、 全長10mmの短冊状のパターンの電流の理論値を求め、それと比較してみましょう。20℃の銅の導電率を1.74×10-8とし、基板の銅の厚さを0.35μmとすると、このパターンの抵抗値はおよそ24.86mΩになり、つまり1Vかけた際の電流は40.23A程度となります。

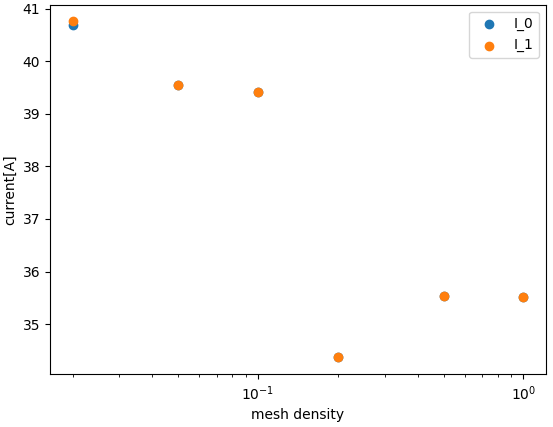

以下の図を見てください。メッシュの細かさを1-0.02の範囲で変化させ、各端子の電流の値をプロットしました。メッシュが十分に細かいとき、電流は40A付近で推移していることが解ると思います。形状が異なるため若干の誤差が出ることは致し方なく、この解析結果にはある程度信憑性があることが確認できます。

図9: メッシュの細かさと電流

今後の展望

もちろん、このプロジェクトは最終目標までに数多くのステップを残しています。次の一歩として取り組みたい事項をいくつか示します。

アダプティブ有限要素法

より精度を向上させる方法として、アダプティブ有限要素法という手法が知られています。これは、より精度が要求される領域において細かくメッシュを切ることで精度を向上させることができます。具体的には、スカラー場の勾配が大きいところなど、値の変化が激しい箇所ではより細かいメッシュを切ると良いです。このアダプティブ有限要素法の実装ですが、現行のFEniCSではこれに対応していないため、一度粗いメッシュで解析を行った結果をもとにメッシュを切り直すことになると思います。

I-Oの拡充

本プロジェクトでは、各端子の電圧を求める機能まで実装を行いました。Y-パラメータを抽出できるところまで実装はしましたが、解析結果をそのままSPICEなどのシミュレーターで用いることはできません。そのため、SPICEモデルやVerilog-Aモデルなどの形でシミュレーターにインポートすることができる形式でデータを出力することが望ましいです。

また、現段階ではスルーホールの座標をもとに境界条件の設定を行っているため、スルーホールを用いない表面実装部品(SMD)を含む基板の解析はできません。しかし、MN-Core BoardなどのターゲットはSMDを多く用いています。そのため、SMDへの対応も重要です。

電磁ノイズ(リアクタンス成分)の解析

本プロジェクトでは、基板の寄生抵抗成分のみを対象にしていましたが、実際には基板の寄生容量や寄生インダクタンスのほうが支配的になる状況も多いです。これらの寄生リアクタンスを解析するには3次元の電磁界の解析を行う必要があり、より大規模な解析を行うことになります。

感想

リモートでの勤務が中心となっていましたが、メンターの方が大変気さくかつ親切に対応してくださり、大変楽しいインターンシップになりました。また、一部オフィスワークの日程も設定されていましたが、ハード部門の部屋で勤務させていただくことができ、大変よい刺激に満ちた、素晴らしい空間を体験することができました。

メンターの山内さん、名村さん、親切に接してくださった皆様、大変ありがとうございました。

最後に

本プロジェクトの成果物はOSSとして公開されることになりました(https://github.com/pfnet/pcb-fem-ohm-sim)。今後も継続的に開発を行い、より良いツールにしていきたいと思います。本ブログを読んで興味を持ってくださった方も是非ご覧になっていただければと思います。

Area